삼성전자는 D램 칩 12개를 쌓은 뒤 수직으로 연결하는 반도체 패키징 기술을 업계 최초로 개발했다고 7일 밝혔다.

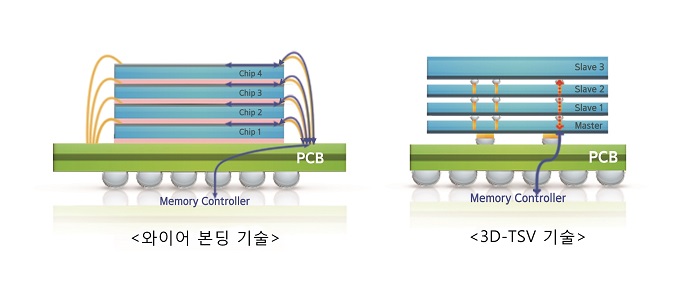

'12단 3차원 실리콘 관통전극(3D-TSV)'으로 불리는 이 기술은 칩 위아래에 머리카락 굵기의 20분의 1 수준의 구멍(전자이동통로) 6만개를 뚫어 칩을 연결하는 첨단 패키징 기술이다.

금선(와이어)을 이용해 칩을 연결하는 기존 방식에 비해 신호를 주고받는 시간이 짧아 소비전력을 획기적으로 줄이는 장점이 있다.

도로에 비유하면 산을 돌아가는 길을 내는 대신 터널을 뚫어 맞은 편으로 신속히 갈 수 있게 한 것과 비슷하다.

삼성전자는 그간 D램 칩 8개를 쌓아 관통하는 기술을 선보였지만 이번에는 그보다 적층수를 늘렸다. 그러면서도 기존과 동일한 패키지 두께를 구현해 고객사가 디자인 변경없이 고용량 제품을 출시할 수 있게 했다.

이 기술에 최신 16기가비트(Gb) D램 칩을 적용하면 업계 최대 용량인 24기가바이트(GB) 고대역폭 메모리(HBM) 제품을 구현할 수 있다고 삼성전자는 설명했다.

백홍주 삼성전자 DS부문 TSP총괄 부사장은 "인공지능, 자율주행, 초고성능 컴퓨팅 시스템 등에서 고성능을 구현할 수 있는 최첨단 패키징 기술이 날로 중요해지고 있다"며 "이 분야에서도 초격차 기술 리더십을 이어가겠다"고 말했다.